#### Features

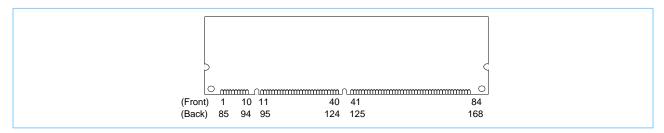

- 168-Pin Registered 8-Byte Dual In-Line Memory Module

- 16Mx72 Synchronous DRAM DIMM

- Performance:

|                   | -260 | -360 | -360 | Units |

|-------------------|------|------|------|-------|

| Device Latency    | 2    | 2    | 3    |       |

| Clock Frequency   | 100  | 66   | 100  | MHz   |

| Clock Access Time | 7.2  | 10.2 | 7.2  | ns    |

- Intended for 66/100MHz and PC100 applications

- Inputs and outputs are LVTTL (3.3V) compatible

- Single 3.3V  $\pm$  0.3V Power Supply

- Single Pulsed RAS interface

- SDRAMs have four internal banks

- Module has one physical bank

- · Fully Synchronous to positive Clock Edge

- Programmable Operation:

- DIMM CAS Latency:3, 4 (Registered mode), 2, 3 (Buffered mode)

- Burst Type: Sequential or Interleave

- Burst Length: 1, 2, 4, 8, Full-Page (Full-Page supports Sequential burst only)

- Operation: Burst Read and Write or Multiple Burst Read with Single Write

- Data Mask for Byte Read/Write control

- Auto Refresh (CBR) and Self Refresh

- Automatic and controlled Precharge Commands

- Suspend Mode and Power Down Mode

- 12/10/2 Addressing (Row/Column/Bank)

- 4096 refresh cycles distributed across 64ms

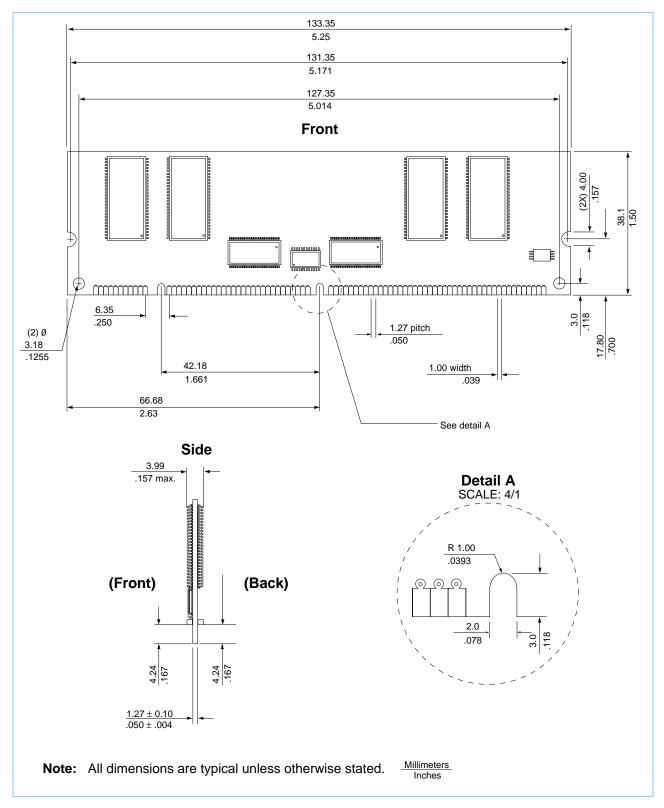

- Card size: 5.25" x 1.5" x 0.157"

- Gold contacts

- SDRAMs in TSOP Type II Package

- Serial Presence Detect with Write protect feature

## Description

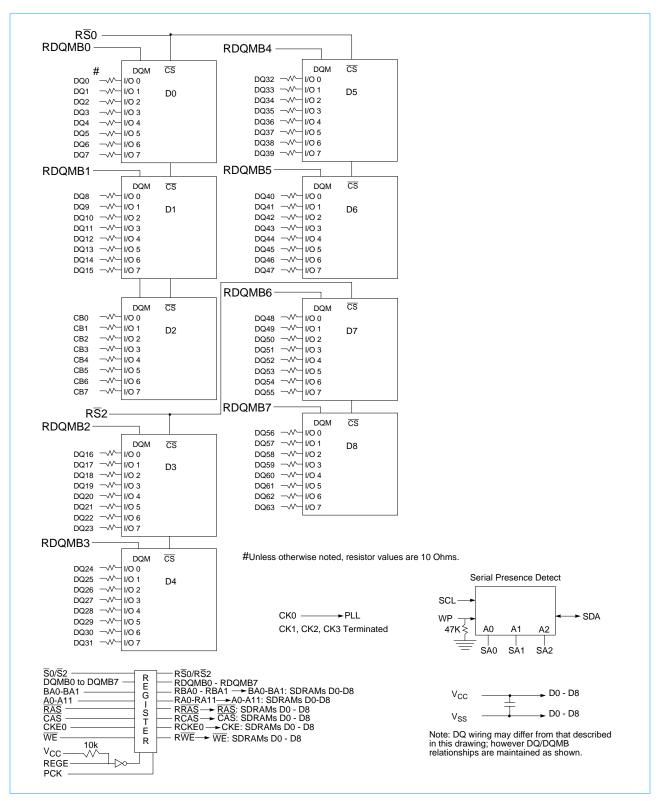

IBM13M16734JCA is a registered 168-Pin Synchronous DRAM Dual In-Line Memory Module (DIMM) organized as a 16Mx72 high-speed memory array. The DIMM uses nine 16Mx8 SDRAMs in 400 mil TSOP packages. The DIMM achieves high-speed data-transfer rates of up to 100 MHz by employing a prefetch/pipeline hybrid architecture that synchronizes the output data to a system clock.

The DIMM is intended for use in applications operating from 66MHz to 100 MHz, PC100, memory bus speeds, and/or heavily loaded bus applications. All control and address signals are re-driven through registers/buffers to the SDRAM devices. The DIMM can be operated in either registered mode (REGE pin tied high), where the control/address input signals are latched in the register on one rising clock edge and sent to the SDRAM devices on the following rising clock edge (data access is delayed by one clock), or in buffered mode (REGE pin tied low) where the input signals pass through the register/buffer to the SDRAM devices on the same clock. XTK simulation models of the DIMM are available to determine which mode to design for.

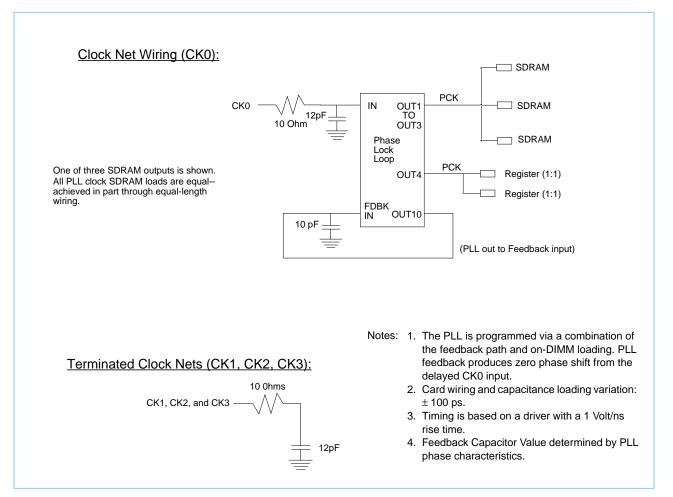

A phase-lock loop (PLL) on the DIMM is used to redrive the clock signals to the SDRAM devices to minimize system clock loading. (CK0 is connected to the PLL, and CK1, CK2, and CK3 are terminated on the DIMM.) A single clock enable (CKE0) controls all devices on the DIMM, enabling the use of SDRAM power-down modes.

Prior to any access operation, the device CAS latency and burst type/length/operation type must be programmed into the DIMM by address inputs A0-A9, A11, BS1 and BA1 using the mode register set cycle. The DIMM CAS latency when operated in buffered mode is the same as the device CAS latency as specified in the SPD EEPROM. The DIMM CAS latency when operated in registered mode is one clock later due to the address and control signals being clocked to the SDRAM devices.

The DIMM uses serial presence detects implemented via a serial EEPROM using the two-pin IIC protocol. The first 128 bytes of serial PD data are programmed and locked by the DIMM manufacturer. The last 128 bytes are available to the customer and may be write protected by providing a high level to pin 81 on the DIMM. An on-board pulldown resistor keeps this in the write-enable mode.

All IBM 168-pin DIMMs provide a high-performance, flexible 8-byte interface in a 5.25" long space-saving footprint.

## **Card Outline**

## **Pin Description**

| CK0 - CK3                                                                                                       | Clock Inputs                | DQ0 - DQ63      | Data Input/Output                           |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|---------------------------------------------|

| CKE0                                                                                                            | Clock Enable                | CB0 - CB7       | Check Bit Data Input/Output                 |

| RAS                                                                                                             | Row Address Strobe          | DQMB0 - DQMB7   | Data Mask                                   |

| CAS                                                                                                             | Column Address Strobe       | V <sub>DD</sub> | Power (3.3V)                                |

| WE                                                                                                              | Write Enable                | V <sub>SS</sub> | Ground                                      |

| <u></u> | Chip Selects                | NC              | No Connect                                  |

| A0 - A9, A11                                                                                                    | Address Inputs              | SCL             | Serial Presence Detect Clock Input          |

| A10/AP                                                                                                          | Address Input/Autoprecharge | SDA             | Serial Presence Detect Data<br>Input/Output |

| BA0, BA1                                                                                                        | SDRAM Bank Address Inputs   | SA0-2           | Serial Presence Detect Address<br>Inputs    |

| WP                                                                                                              | SPD Write Protect           | REGE            | Register Enable                             |

#### IBM13M16734JCA 16M x 72 1 Bank Registered/Buffered SDRAM Module

## Pinout

| Pin | Front           | Pin | Back            | Pin | Front           | Pin | Back            | Pin | Front           | Pin | Back            | Pin | Front    | Pin | Back     |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|-----|----------|-----|----------|

| #   | Side            | #   | Side     | #   | Side     |

| 1   | V <sub>SS</sub> | 85  | V <sub>SS</sub> | 22  | CB1             | 106 | CB5             | 43  | V <sub>SS</sub> | 127 | V <sub>SS</sub> | 64  | $V_{SS}$ | 148 | $V_{SS}$ |

| 2   | DQ0             | 86  | DQ32            | 23  | V <sub>SS</sub> | 107 | V <sub>SS</sub> | 44  | NC              | 128 | CKE0            | 65  | DQ21     | 149 | DQ53     |

| 3   | DQ1             | 87  | DQ33            | 24  | NC              | 108 | NC              | 45  | <del>S</del> 2  | 129 | NC              | 66  | DQ22     | 150 | DQ54     |

| 4   | DQ2             | 88  | DQ34            | 25  | NC              | 109 | NC              | 46  | DQMB2           | 130 | DQMB6           | 67  | DQ23     | 151 | DQ55     |

| 5   | DQ3             | 89  | DQ35            | 26  | V <sub>DD</sub> | 110 | V <sub>DD</sub> | 47  | DQMB3           | 131 | DQMB7           | 68  | $V_{SS}$ | 152 | $V_{SS}$ |

| 6   | V <sub>DD</sub> | 90  | V <sub>DD</sub> | 27  | WE              | 111 | CAS             | 48  | NC              | 132 | NC              | 69  | DQ24     | 153 | DQ56     |

| 7   | DQ4             | 91  | DQ36            | 28  | DQMB0           | 112 | DQMB4           | 49  | V <sub>DD</sub> | 133 | V <sub>DD</sub> | 70  | DQ25     | 154 | DQ57     |

| 8   | DQ5             | 92  | DQ37            | 29  | DQMB1           | 113 | DQMB5           | 50  | NC              | 134 | NC              | 71  | DQ26     | 155 | DQ58     |

| 9   | DQ6             | 93  | DQ38            | 30  | S0              | 114 | NC              | 51  | NC              | 135 | NC              | 72  | DQ27     | 156 | DQ59     |

| 10  | DQ7             | 94  | DQ39            | 31  | NC              | 115 | RAS             | 52  | CB2             | 136 | CB6             | 73  | $V_{DD}$ | 157 | $V_{DD}$ |

| 11  | DQ8             | 95  | DQ40            | 32  | V <sub>SS</sub> | 116 | V <sub>SS</sub> | 53  | CB3             | 137 | CB7             | 74  | DQ28     | 158 | DQ60     |

| 12  | V <sub>SS</sub> | 96  | V <sub>SS</sub> | 33  | A0              | 117 | A1              | 54  | V <sub>SS</sub> | 138 | V <sub>SS</sub> | 75  | DQ29     | 159 | DQ61     |

| 13  | DQ9             | 97  | DQ41            | 34  | A2              | 118 | A3              | 55  | DQ16            | 139 | DQ48            | 76  | DQ30     | 160 | DQ62     |

| 14  | DQ10            | 98  | DQ42            | 35  | A4              | 119 | A5              | 56  | DQ17            | 140 | DQ49            | 77  | DQ31     | 161 | DQ63     |

| 15  | DQ11            | 99  | DQ43            | 36  | A6              | 120 | A7              | 57  | DQ18            | 141 | DQ50            | 78  | $V_{SS}$ | 162 | $V_{SS}$ |

| 16  | DQ12            | 100 | DQ44            | 37  | A8              | 121 | A9              | 58  | DQ19            | 142 | DQ51            | 79  | CK2      | 163 | СКЗ      |

| 17  | DQ13            | 101 | DQ45            | 38  | A10/AP          | 122 | BA0             | 59  | V <sub>DD</sub> | 143 | V <sub>DD</sub> | 80  | NC       | 164 | NC       |

| 18  | V <sub>DD</sub> | 102 | V <sub>DD</sub> | 39  | BA1             | 123 | A11             | 60  | DQ20            | 144 | DQ52            | 81  | WP       | 165 | SA0      |

| 19  | DQ14            | 103 | DQ46            | 40  | V <sub>DD</sub> | 124 | V <sub>DD</sub> | 61  | NC              | 145 | NC              | 82  | SDA      | 166 | SA1      |

| 20  | DQ15            | 104 | DQ47            | 41  | V <sub>DD</sub> | 125 | CK1             | 62  | NC              |     | NC              | 83  | SCL      | 167 | SA2      |

| 21  | CB0             | 105 | CB4             | 42  | CK0             | 126 | NC              | 63  | NC              | 147 | REGE            | 84  | $V_{DD}$ | 168 | $V_{DD}$ |

Note: All pin assignments are consistent with all 8-byte unbuffered versions.

## **Ordering Information**

| Part Number         | Organization | Clock Cycle | CAS Latency | Access Time | Leads | Dimension             | Power |

|---------------------|--------------|-------------|-------------|-------------|-------|-----------------------|-------|

| IBM13M16734JCA-260T | 16Mx72       | 10-20       | 2           | 6.0ns       | Cold  |                       | 3.3V  |

| IBM13M16734JCA-360T | TOIVIX72     | 10ns        | 3           | 6.0ns       | Gold  | 5.25" x 1.5" x 0.157" |       |

### x72 ECC SDRAM DIMM Block Diagram (1 Bank, x8 SDRAMs)

©IBM Corporation. All rights reserved. Use is further subject to the provisions at the end of this document.

## **Clock Wiring**

# Input/Output Functional Description

| Symbol                                                  | Туре            | Signal | Polarity                                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------|-----------------|--------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK0 - CK3                                               | Input           | Pulse  | Positive<br>Edge                                 | The system clock inputs. All the SDRAM inputs are sampled on the rising edge of their associated clock. CK0 drives the PLL. CK1, CK2, and CK3 are terminated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CKE0                                                    | Input           | Level  | Active<br>High                                   | Activates the SDRAM CK signal when high and deactivates the CK signal when low. By deactivating the clocks, CKE low initiates the Power Down mode, the Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <u></u> \$0, \$2                                        | Input           | Pulse  | Active<br>Low                                    | Enables the associated SDRAM command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $\frac{\overline{RAS},}{\overline{CAS}\;\overline{WE}}$ | Input           | Pulse  | Active<br>Low                                    | When sampled at the positive rising edge of the clock, $\overline{CAS}$ , $\overline{RAS}$ , and $\overline{WE}$ define the operation to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BA0, 1                                                  | Input           | Level  | —                                                | Selects which SDRAM bank of four is activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A0 - A9,<br>A11,<br>A10/AP                              | Input           | Level  | _                                                | During a Bank Activate command cycle, A0-A11 defines the row address (RA0-RA11) when sampled at the rising clock edge.<br>During a Read or Write command cycle, A0-A9 defines the column address (CA0-CA9) when sampled at the rising clock edge. In addition to the column address, AP is used to invoke auto-precharge operation at the end of the burst read or write cycle. If AP is high, autoprecharge is selected and BA0, BA1 defines the bank to be precharged. If AP is low, autoprecharge is disabled.<br>During a Precharge command cycle, AP is used in conjunction with BA0, BA1 to control which bank(s) to precharge. If AP is high, all banks will be precharged regardless of the state of BA0 or BA1. If AP is low, then BA0 and BA1 are used to define which bank to precharge. |

| DQ0 -<br>DQ63,<br>CB0 - CB7                             | Input<br>Output | Level  |                                                  | Data and Check Bit Input/Output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DQMB0 -<br>DQMB7                                        | Input           | Pulse  | Active<br>High                                   | The Data Input/Output masks, associated with one data byte, place the DQ buffers in a high impedance state when sampled high. In Read mode, DQMB has a latency of two clock cycles in Buffered mode or three clock cycles in Registered mode, and controls the output buffers like an output enable.<br>In Write mode, DQMB has a zero clock latency in Buffered mode and a latency of one clock cycle in Registered mode. In this case, DQMB operates as a byte mask by allowing input data to be written if it is low but blocks the write operation if it is high.                                                                                                                                                                                                                               |

| $V_{DD}, V_{SS}$                                        | Supply          |        |                                                  | Power and ground for the module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| REGE                                                    | Input           | Level  | Active<br>High<br>(Regis-<br>ter Mode<br>Enable) | The Register Enable pin is used to permit the DIMM to operate in Buffered mode (inputs re-<br>driven asynchronously) or Registered mode (signals re-driven to SDRAMs when clock rises, and<br>held valid until next rising clock).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SA0 - 2                                                 | Input           | Level  | —                                                | These signals are tied at the system planar to either $V_{SS}$ or $V_{DD}$ to configure the SPD EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDA                                                     | Input<br>Output | Level  | _                                                | This is a bidirectional pin used to transfer data into or out of the SPD EEPROM. A resistor must be connected from the SDA bus line to $V_{\text{DD}}$ to act as a pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SCL                                                     | Input           | Pulse  | _                                                | This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected from the SCL bus line to $V_{DD}$ to act as a pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| WP                                                      | Input           | Level  | Active<br>High                                   | This signal is pulled low on the DIMM to enable data to be written into the last 128 bytes of the SPD EEPROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### IBM13M16734JCA 16M x 72 1 Bank Registered/Buffered SDRAM Module

## Serial Presence Detect (Part 1 of 2)

| Byte #  | Description                                               |                                                         | SPD Entry Value                 | Serial PD Data Entry<br>(Hexadecimal) | Notes |

|---------|-----------------------------------------------------------|---------------------------------------------------------|---------------------------------|---------------------------------------|-------|

| 0       | Number of Serial PD Bytes Written during Production       | า                                                       | 128                             | 80                                    |       |

| 1       | Total Number of Bytes in Serial PD device                 |                                                         | 256                             | 08                                    |       |

| 2       | Fundamental Memory Type                                   |                                                         | SDRAM                           | 04                                    |       |

| 3       | Number of Row Addresses on Assembly                       |                                                         | 12                              | 0C                                    |       |

| 4       | Number of Column Addresses on Assembly                    |                                                         | 10                              | 0A                                    |       |

| 5       | Number of DIMM Banks                                      |                                                         | 1                               | 01                                    |       |

| 6 - 7   | Data Width of Assembly                                    |                                                         | x72                             | 4800                                  |       |

| 8       | Assembly Voltage Interface Levels                         |                                                         | LVTTL                           | 01                                    |       |

| 9       | SDRAM Device Cycle Time (CL = 3)                          |                                                         | 10.0ns                          | A0                                    | 1, 2  |

| 4.0     |                                                           | -260                                                    | 6.0ns                           | 60                                    |       |

| 10      | SDRAM Device Access Time from Clock at CL=3               | -360                                                    | 6.0ns                           | 60                                    |       |

| 11      | DIMM Configuration Type                                   |                                                         | ECC                             | 02                                    |       |

| 12      | Assembly Refresh Rate/Type                                | SR/1X(15.625us)                                         | 80                              |                                       |       |

| 13      | SDRAM Device Width                                        |                                                         | x8                              | 08                                    |       |

| 14      | Error Checking SDRAM Device Width                         |                                                         | x8                              | 08                                    |       |

| 15      | SDRAM Device Attr: Min Clk Delay, Random Col Ac           | cess                                                    | 1 Clock                         | 01                                    |       |

| 16      | SDRAM Device Attributes: Burst Lengths Supported          |                                                         | 1, 2, 4, 8, Full Page           | 8F                                    |       |

| 17      | SDRAM Device Attributes: Number of Device Banks           |                                                         | 4                               | 04                                    |       |

| 18      | SDRAM Device Attributes: CAS Latency                      |                                                         | 2, 3                            | 06                                    |       |

| 19      | SDRAM Device Attributes: CS Latency                       |                                                         | 0                               | 01                                    |       |

| 20      | SDRAM Device Attributes: WE Latency                       |                                                         | 0                               | 01                                    |       |

| 21      | SDRAM Module Attributes                                   |                                                         | Registered/Buffered with<br>PLL | IF                                    |       |

| 22      | SDRAM Device Attributes: General                          | Write-1/Read Burst,<br>Precharge All,<br>Auto-Precharge | 0E                              |                                       |       |

|         |                                                           | -260                                                    | 10.0ns                          | A0                                    | 1, 2  |

| 23      | Minimum Clock Cycle at CLX-1 (CL = 2)                     | -360                                                    | 15.0ns                          | F0                                    |       |

| <u></u> | Maximum Data Access Time (t <sub>AC</sub> ) from Clock at | -260                                                    | 6.0ns                           | 60                                    |       |

| 24      | CLX-1 (CL = 2)                                            | -360                                                    | 9.0ns                           | 90                                    |       |

1. In a registered DIMM, data is delayed an additional clock cycle due to the on-DIMM pipeline register (that is, Device CL [clock cycles] + 1 = DIMM CAS latency).

2. Minimum application clock cycle time for the -260 and -360 is 10ns (100MHz)

3. cc = Checksum Data byte, 00-FF (Hex).

- 4. "R" = Alphanumeric revision code, A-Z, 0-9.

- 5. rr = ASCII coded revision code byte "R".

6. ww = Binary coded decimal week code, 01-53 (Decimal) → 01-35 (Hex).

7. yy = Binary coded decimal year code, 00-99 (Decimal) → 00-63 (Hex).

8. ss = Serial number data byte, 00-FF (Hex).

### Serial Presence Detect (Part 2 of 2)

| Byte #    | Description                                                            |           | SPD Entry Value                | Serial PD Data Entry<br>(Hexadecimal)    | Notes |

|-----------|------------------------------------------------------------------------|-----------|--------------------------------|------------------------------------------|-------|

| 25        | Minimum Clock Cycle Time at CLX-2 (CL = 1)                             |           | N/A                            | 00                                       |       |

| 26        | Maximum Data Access Time $(t_{AC})$ from Clock at CL> 1)               | <-2 (CL = | N/A                            | 00                                       |       |

| 27        | Minimum Row Precharge Time (t <sub>RP</sub> )                          |           | 20.0ns                         | 14                                       |       |

| 28        | Minimum Row Active to Row Active delay (t <sub>RRD</sub> )             |           | 20.0ns                         | 14                                       |       |

| 29        | Minimum $\overline{RAS}$ to $\overline{CAS}$ delay (t <sub>RCD</sub> ) |           | 20.0ns                         | 14                                       |       |

| 30        | Minimum RAS Pulse width (t <sub>RAS</sub> )                            |           | 50.0ns                         | 32                                       |       |

| 31        | Module Bank Density                                                    |           | 128MB                          | 20                                       |       |

| 32        | Address and Command Setup Time Before Clock                            |           | 2.0ns                          | 20                                       |       |

| 33        | Address and Command Hold Time After Clock                              |           | 1.0ns                          | 10                                       |       |

| 34        | Data Input Setup Time Before Clock                                     | 2.0ns     | 20                             |                                          |       |

| 35        | Data Input Hold Time After Clock                                       | 1.0ns     | 10                             |                                          |       |

| 36 - 61   | Reserved                                                               | Undefined | 00                             |                                          |       |

| 62        | SPD Revision                                                           |           | PC100 1.2A                     | 12                                       |       |

| 63        | Checksum for bytes 0 - 62                                              |           | Checksum Data                  | сс                                       | 3     |

| 64 - 71   | Manufacturers' JEDEC ID Code                                           |           | IBM                            | A4000000000000000                        |       |

| 72        | Accomply Manufacturing Logotian                                        |           | Toronto, Canada                | 91                                       |       |

| 12        | Assembly Manufacturing Location                                        |           | Vimercate, Italy               | 53                                       |       |

| 70 00     | Assessed by Dard Neuropean                                             | -260      | ASCII '13M16734JC"R"<br>-260T' | 31334D31363733344A43<br>2D32363054202020 | 4.5   |

| 73 - 90   | Assembly Part Number                                                   | -360      | ASCII '13M16734JC"R"<br>-360T' | 31334D31363733344A43<br>2D33363054202020 | 4, 5  |

| 91 - 92   | Assembly Revision Code                                                 |           | "R" plus ASCII blank           | rr20                                     | 5     |

| 93 - 94   | Assembly Manufacturing Date                                            |           | Year/Week Code                 | ууww                                     | 6, 7  |

| 95 - 98   | Assembly Serial Number                                                 |           | Serial Number                  | SSSSSSS                                  | 8     |

| 99 - 125  | Reserved                                                               |           | Undefined                      | Not Specified                            |       |

| 126       | Module Supports this Clock Frequency                                   |           | 100MHz                         | 64                                       |       |

| 107       | Attributes for cleak frequency defined in Pute 196                     | -260      | CLK0; CL=2, 3; ConAP           | 87                                       |       |

| 127       | Attributes for clock frequency defined in Byte 126                     | -360      | CLK0; CL= 3; ConAP             | 85                                       |       |

| 128 - 255 | Open for Customer Use                                                  |           | Undefined                      | 00                                       |       |

1. In a registered DIMM, data is delayed an additional clock cycle due to the on-DIMM pipeline register (that is, Device CL [clock cycles] + 1 = DIMM CAS latency).

2. Minimum application clock cycle time for the -260 and -360 is 10ns (100MHz)

3. cc = Checksum Data byte, 00-FF (Hex).

4. "R" = Alphanumeric revision code, A-Z, 0-9.

5. rr = ASCII coded revision code byte "R".

6. ww = Binary coded decimal week code, 01-53 (Decimal) → 01-35 (Hex).

7. yy = Binary coded decimal year code, 00-99 (Decimal) → 00-63 (Hex).

8. ss = Serial number data byte, 00-FF (Hex).

## **Absolute Maximum Ratings**

| Symbol           | Parameter                       |                  | Rating              | V<br>°C<br>°C | Notes |

|------------------|---------------------------------|------------------|---------------------|---------------|-------|

| V <sub>DD</sub>  | Power Supply Voltage            |                  | -0.3 to +4.6        |               |       |

|                  |                                 | SDRAM Devices    | -1.0 to +4.6        |               |       |

| N/               |                                 | Serial PD Device | -0.3 to +6.5        |               |       |

| V <sub>IN</sub>  | Input Voltage                   | Register         | 0 - V <sub>DD</sub> | V             | 1     |

|                  |                                 | PLL              | 0 - V <sub>DD</sub> |               |       |

| V                |                                 | SDRAM Devices    | -1.0 to +4.6        |               |       |

| V <sub>OUT</sub> | Output Voltage                  | Serial PD Device | -0.3 to +6.5        |               |       |

| T <sub>A</sub>   | Operating Temperature (ambient) |                  | 0 to +70            | °C            | 1     |

| T <sub>STG</sub> | Storage Temperature             |                  | -55 to +125         | °C            | 1     |

| PD               | Power Dissipation               |                  | 6.3                 | W             | 1, 2  |

| I <sub>OUT</sub> | Short Circuit Output Current    |                  | 50                  | mA            | 1     |

| F <sub>MIN</sub> | Minimum Operating Frequency     |                  | 66                  | MHz           |       |

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Maximum power is calculated assuming the physical bank is in Auto Refresh Mode.

## **Recommended DC Operating Conditions** (T<sub>A</sub>= 0 to 70°C)

| Symbol          | Parameter          |      | Rating | Units                 | Nataa |       |

|-----------------|--------------------|------|--------|-----------------------|-------|-------|

|                 |                    | Min. | Тур.   | Max.                  | Units | Notes |

| V <sub>DD</sub> | Supply Voltage     | 3.0  | 3.3    | 3.6                   | V     | 1     |

| $V_{\text{IH}}$ | Input High Voltage | 2.0  | _      | V <sub>DD</sub> + 0.3 | V     | 1     |

| V <sub>IL</sub> | Input Low Voltage  | -0.3 | _      | 0.8                   | V     | 1     |

1. All voltages referenced to  $V_{SS}$ .

| Currente al      | Description                                                            | Organization | Linita |

|------------------|------------------------------------------------------------------------|--------------|--------|

| Symbol           | Parameter                                                              | x72 Max      | Units  |

| C <sub>I1</sub>  | Input Capacitance (A0 - A9, A10/AP, A11, BA0, BA1, RAS, CAS, WE, CKE0) | 11.5         | pF     |

| C <sub>I2</sub>  | Input Capacitance (S0, S2)                                             | 9.0          | pF     |

| C <sub>I3</sub>  | Input Capacitance (CK0)                                                | 28           | pF     |

| C <sub>14</sub>  | Input Capacitance (DQMB0 - DQMB7)                                      | 9.5          | pF     |

| C <sub>I5</sub>  | Input Capacitance (SA0 - SA2, SCL, WP)                                 | 9            | pF     |

| C <sub>I6</sub>  | Input Capacitance (REGE)                                               | 10           | pF     |

| C <sub>I7</sub>  | Input Capacitance (CK1 - CK3)                                          | 16           | pF     |

| C <sub>IO1</sub> | Input/Output Capacitance (DQ0 - DQ63, CB0 - CB7)                       | 16           | pF     |

| C <sub>IO2</sub> | Input/Output Capacitance (SDA)                                         | 11           | pF     |

# **Capacitance** (T<sub>A</sub>= 25°C, f=1MHz, V<sub>DD</sub>= $3.3V \pm 0.3V$ )

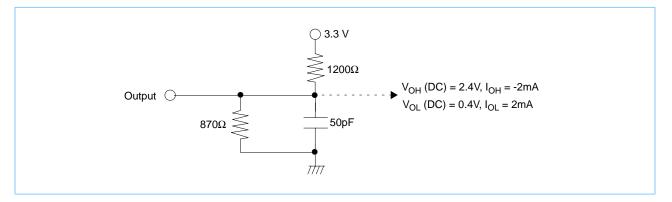

## **Device DC Output Load Circuit**

# Input/Output Characteristics (T<sub>A</sub>= 0 to +70°C, V<sub>DD</sub>= $3.3V \pm 0.3V$ )

|                   | $(L) = \begin{cases} \text{Input Leakage Current, any input} \\ (0.0V \le V_{\text{IN}} \le 3.6V), \text{ All Other Pins} \\ \text{Not Under Test} = 0V \end{cases} \qquad \begin{array}{l} \text{Address and Control Inputs} \\ \text{DQ0-63, CB0 - 7} \\ \text{DQ0-63, CB0 - 7} \\ \text{DQ0-63, CB0 - 7} \\ \text{Output Leakage Current} \\ \text{OUT} \text{ is disabled, } 0.0V \le V_{\text{OUT}} \le 3.6V) \\ \hline \text{SDA} \\ \end{array}$ |                 | х    | 72   |       |      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|------|-------|------|

| Symbol            |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ter             | Min. | Max. | Units | Note |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • • • • •       |      | 10   |       |      |

| I <sub>I(L)</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DQ0-63, CB0 - 7 | -2   | +2   | μA    |      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DQ0-63, CB0 - 7 | -2   | +2   |       |      |

| IO(L)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SDA             | -1   | +1   | μA    |      |

| V <sub>OH</sub>   | Output Level<br>Output "H" Level Voltage (I <sub>OUT</sub> = -2.0mA)                                                                                                                                                                                                                                                                                                                                                                                    |                 |      |      |       | 4    |

| V <sub>OL</sub>   | Output Level<br>Output "L" Level Voltage (I <sub>OUT</sub> = +2.0mA)                                                                                                                                                                                                                                                                                                                                                                                    |                 | 0.0  | 0.4  | V     | 1    |

# Operating, Standby, and Refresh Currents (T\_A= 0 to +70 $^{\circ}\text{C},$ V\_DD= 3.3V $\pm$ 0.3V)

| Devenuetor                                       | Cumbal             | Track Orac division                                                                                                                                                                                                                       | Clock | Cycle | l lucita | Natas |  |

|--------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|----------|-------|--|

| Parameter                                        | Symbol             | Test Condition                                                                                                                                                                                                                            | 10ns  | 15ns  | Units    | Notes |  |

| Operating Current<br>1 bank operation            | I <sub>CC1</sub>   | $t_{RC} = t_{RC}(min), t_{CK} = min$<br>Active-Precharge command cycling<br>without burst operation                                                                                                                                       | 891   | 712   | mA       | 1, 2  |  |

| Precharge Standby Current in                     | I <sub>CC2P</sub>  | $eq:cked_cked_cked_cked_cked_cked_cked_cked_$                                                                                                                                                                                             | 180   | 136   | mA       | 1     |  |

| Power Down Mode                                  | I <sub>CC2PS</sub> | $\begin{split} \label{eq:cke0} CKE0 &\leq V_{IL} \mbox{ (max), } t_{CK} \mbox{ = Infinity,} \\ \hline S0, \ensuremath{\overline{S}2} \mbox{ = V}_{IH} \mbox{ (min)} \end{split}$                                                          | 34    | 34    | mA       |       |  |

| Precharge Standby Current in                     | I <sub>CC2</sub>   | $\begin{split} \label{eq:cked} CKE0 &\geq V_{IH} \text{ (min), } t_{CK} = \text{min,} \\ \overline{S}0, \ \overline{S}2 = V_{IH} \text{ (min)} \end{split}$                                                                               | 486   | 334   | mA       | 1     |  |

| Non-Power Down Mode                              | I <sub>CC2S</sub>  | $\begin{split} \label{eq:ckeo} CKE0 &\geq V_{IH} \mbox{ (min), } t_{CK} = \mbox{Infinity,} \\ \hline \overline{S}0, \ \overline{S}2 = V_{IH} \mbox{ (min)} \end{split}$                                                                   | 115   | 115   | mA       |       |  |

|                                                  | I <sub>CC3</sub>   | $\begin{split} \label{eq:cked} CKE0 &\geq V_{IH} \text{ (min), } t_{CK} = \text{min,} \\ \overline{S}0, \ \overline{S}2 = V_{IH} \text{ (min)} \end{split}$                                                                               | 531   | 487   | mA       | 1     |  |

| No Operating Current<br>(Active state: 4bank)    | I <sub>CC3P</sub>  | $\begin{split} \text{CKE0} &\leq \text{V}_{\text{IL}} \text{ (max), } \text{t}_{\text{CK}} = \text{min,} \\ &\overline{\text{S0}}, \ \overline{\text{S2}} = \text{V}_{\text{IH}} \text{ (min)} \\ & (\text{Power Down Mode}) \end{split}$ | 261   | 217   | mA       | 1     |  |

| Burst Operating Current<br>(Active state: 4bank) | I <sub>CC4</sub>   | t <sub>CK</sub> = min,<br>Read command cycling                                                                                                                                                                                            | 981   | 667   | mA       | 1, 2  |  |

| Auto (CBR) Refresh Current                       | I <sub>CC5</sub>   | t <sub>CK</sub> = min,<br>CBR command cycling                                                                                                                                                                                             | 1748  | 1432  | mA       | 1     |  |

| Self Refresh Current                             | I <sub>CC6</sub>   | CKE0 ≤ 0.2V                                                                                                                                                                                                                               | 43    | 43    | mA       |       |  |

1. These parameters depend on the cycle rate and are measured with the cycle determined by the minimum value of t<sub>CK</sub> and t<sub>RC</sub>. Input signals are changed once during  $t_{CK}(min)$ .  $t_{CK}(min) = 10$ ns or 15ns. 2. The specified values are obtained with the DIMM data outputs open.

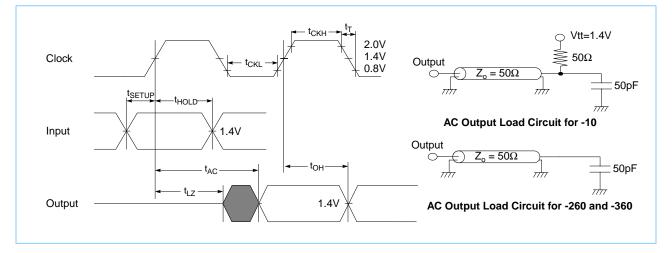

### AC Characteristics ( $T_A$ = 0 to +70°C, $V_{DD}$ = 3.3V ± 0.3V)

- 1. An initial pause of 200μs, with CKE0 held high, is required after power-up. A Precharge All Banks command must be given followed by a minimum of eight Auto (CBR) Refresh cycles before or after the Mode Register Set operation.

- 2. AC timing tests have  $V_{IL} = 0.8V$  and  $V_{IH} = 2.0V$  with the timing referenced to the 1.40V crossover point.

- 3. The Transition time is measured between  $V_{IH}$  and  $V_{IL}$  (or between  $V_{IL}$  and  $V_{IH}$ ).

- 4. AC measurements assume  $t_T=1.2ns$  (1 Volt/ns rise).

- 5. In addition to meeting the transition rate specification, the clock and CKE must transit between  $V_{IH}$  and  $V_{IL}$  (or between  $V_{IL}$  and  $V_{IH}$ ) in a monotonic manner

- 6. A 1 ms stabilization time is required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal.

### **AC Characteristics Diagrams**

### **Clock and Clock Enable Parameters**

| Symbol           | Parameter                                            |            | -260, (Device CL,<br>t <sub>RCD</sub> , t <sub>RP</sub> = 2, 2, 2) |      | -360, (Device CL,<br>t <sub>RCD</sub> , t <sub>RP</sub> = 3, 2, 2) |      | Units | Notes |

|------------------|------------------------------------------------------|------------|--------------------------------------------------------------------|------|--------------------------------------------------------------------|------|-------|-------|

|                  |                                                      |            | Min.                                                               | Max. | Min.                                                               | Max. |       |       |

| t <sub>CK4</sub> | Clock Cycle Time, DIMM $\overline{CAS}$ Latency = 4  | Registered | 10                                                                 | 1000 | 10                                                                 | 1000 | ns    | 1     |

|                  |                                                      | Registered | 10                                                                 | 1000 | 15                                                                 | 1000 | ns    | 1.0   |

| t <sub>CK3</sub> | Clock Cycle Time, DIMM $\overline{CAS}$ Latency = 3  | Buffered   | 10                                                                 | 1000 | 10                                                                 | 1000 | ns    | 1, 2  |

| t <sub>CK2</sub> | Clock Cycle Time, DIMM $\overline{CAS}$ Latency = 2  | Buffered   | 10                                                                 | 1000 | 15                                                                 | 1000 | ns    | 1     |

| t <sub>AC4</sub> | Clock Access Time, DIMM $\overline{CAS}$ Latency = 4 | Registered | _                                                                  | 7.2  | _                                                                  | 7.2  | ns    | 1, 3  |

|                  |                                                      |            | _                                                                  | 7.2  | _                                                                  | 10.2 | ns    | 4.0   |

| t <sub>AC3</sub> | Clock Access Time, DIMM CAS Latency = 3              | Buffered   | _                                                                  | 7.2  | _                                                                  | 7.2  | ns    | 1, 3  |

| t <sub>AC2</sub> | Clock Access Time, DIMM $\overline{CAS}$ Latency = 2 | Buffered   | _                                                                  | 7.2  | _                                                                  | 10.2 | ns    | 1, 3  |

| t <sub>CKH</sub> | Clock High Pulse Width                               |            | 3                                                                  | _    | 3                                                                  | _    | ns    | 4     |

| t <sub>CKL</sub> | Clock Low Pulse Width                                |            | 3                                                                  | _    | 3                                                                  | _    | ns    | 4     |

|                  |                                                      | Registered | 2.1                                                                | _    | 2.1                                                                | _    | ns    |       |

| t <sub>CES</sub> | Clock Enable Set-up Time                             | Buffered   | 7.4                                                                | _    | 7.4                                                                | _    | ns    | 1     |

| +                | Olash Fashla Hald Tires                              | Registered | 1.5                                                                | —    | 1.5                                                                | _    | ns    | 1     |

| t <sub>CEH</sub> | Clock Enable Hold Time                               | Buffered   | 0.0                                                                | —    | 0.0                                                                |      | ns    |       |

| t <sub>SB</sub>  | Power Down mode Entry Time                           |            | 0                                                                  | 10   | 0                                                                  | 10   | ns    |       |

| t <sub>T</sub>   | Transition Time (Rise and Fall)                      |            | 0.5                                                                | 10   | 0.5                                                                | 10   | ns    |       |

1. DIMM CAS latency = device CL [clock cycles] + 1 for Register mode; DIMM CAS latency is one clock less for Buffer mode.

2. For 66Mhz clock, DIMM  $\overline{CAS}$  Latency = 3 is the standard application.

3. Access time is measured at 1.4V. See AC output load circuit.

t<sub>CKH</sub> is the pulse width of CLK measured from the positive edge to the negative edge referenced to V<sub>IH</sub> (min). t<sub>CKL</sub> is the pulse width of CLK measured from the negative edge to the positive edge referenced to V<sub>IL</sub> (max).

### **Common Parameters**

| Current al       | Parameter                                                   |            | -260 |        | -360 |        | Linite | Natas |  |

|------------------|-------------------------------------------------------------|------------|------|--------|------|--------|--------|-------|--|

| Symbol           |                                                             |            | Min. | Max.   | Min. | Max.   | Units  | Notes |  |

| ÷                | Commond Codus Time                                          | Registered | 2.1  |        | 2.1  |        | ns     | 1     |  |

| t <sub>CS</sub>  | Command Setup Time                                          | Buffered   | 7.4  |        | 7.4  |        | ns     | - 1   |  |

| ÷                | Common di la la Timo                                        | Registered | 1.5  |        | 1.5  |        | ns     | 1     |  |

| t <sub>CH</sub>  | Command Hold Time                                           | Buffered   | 0.0  |        | 0.0  |        | ns     | I     |  |

| ÷                | Address and Dark Calest Cature Time                         | Registered | 2.1  |        | 2.1  |        | ns     | 1     |  |

| t <sub>AS</sub>  | Address and Bank Select Set-up Time                         | Buffered   | 7.4  |        | 7.4  |        | ns     |       |  |

| ÷                | Address and Dark Calest Hald Time                           | Registered | 1.5  |        | 1.5  |        | ns     | 1     |  |

| t <sub>AH</sub>  | Address and Bank Select Hold Time                           | Buffered   | 0.0  |        | 0.0  |        | ns     | I     |  |

| t <sub>RCD</sub> | RAS to CAS Delay                                            |            | 20   |        | 20   |        | ns     | 2     |  |

| t <sub>RC</sub>  | Bank Cycle Time                                             |            | 70   |        | 70   |        | ns     | 2     |  |

| t <sub>RAS</sub> | Active Command Period                                       |            | 50   | 100000 | 50   | 100000 | ns     | 2     |  |

| t <sub>RP</sub>  | Precharge Time                                              |            | 20   |        | 20   |        | ns     | 2     |  |

| t <sub>RRD</sub> | Bank to Bank Delay Time                                     |            | 20   |        | 20   |        | ns     | 2     |  |

| t <sub>CCD</sub> | $\overline{CAS}$ to $\overline{CAS}$ Delay Time (Same Bank) |            | 1    |        | 1    |        | CLK    |       |  |

1. The setup and hold times refer to the addition of the register. Note that although the Buffered setup times appear much greater, there is no additional clock cycle as there is in Registered mode.

2. These parameters account for the number of clock cycles and depend on the operating frequency of the clock as follows: the number of clock cycles = specified value of timing/clock period (count fractions as a whole number).

## Mode Register Set Cycle

| Currents al      | Parameter                    | -2   | 60   | -3   | 60   | Units | Natas |

|------------------|------------------------------|------|------|------|------|-------|-------|

| Symbol           |                              | Min. | Max. | Min. | Max. |       | Notes |

| t <sub>RSC</sub> | Mode Register Set Cycle Time | 20   | —    | 20   | —    | ns    |       |

## **Refresh Cycle**

| Symbol            | Parameter              | -2   | 60   | -3   | 60   | Units | Natas |  |

|-------------------|------------------------|------|------|------|------|-------|-------|--|

|                   |                        | Min. | Max. | Min. | Max. |       | Notes |  |

| t <sub>SREX</sub> | Self Refresh Exit Time | 10   | _    | 10   | _    | CLK   | 1     |  |

| t <sub>REF</sub>  | Refresh Period         | —    | 64   | _    | 64   | ms    |       |  |

| 1. 4096           | 1. 4096 cycles.        |      |      |      |      |       |       |  |

## **Read Cycle**

| Currente al      | Parameter                             |            | -260 |      | -360 |      | l luite | Neter |

|------------------|---------------------------------------|------------|------|------|------|------|---------|-------|

| Symbol           |                                       |            | Min. | Max. | Min. | Max. | Units   | Notes |

| t <sub>ОН</sub>  | Data Out Hold Time                    |            | 3.6  |      | 3.6  |      | ns      | 1     |

| t <sub>LZ</sub>  | Data Out to Low Impedance Time        |            | 0.6  |      | 0.6  |      | ns      |       |

| t <sub>HZ3</sub> | Data Out to High Impedance Time       |            | 3.6  | 7.2  | 3.6  | 7.2  | ns      | 1     |

| t <sub>HZ2</sub> | Data Out to High Impedance Time       |            | 3.6  | 7.2  | 3.6  | 9.2  | ns      | 1     |

| +                | DOM Data Out Dischla Latanau          | Registered | 3    |      | 3    |      | CLK     |       |

| t <sub>DQZ</sub> | DQM Data Out Disable Latency Buffered |            | 2    |      | 2    |      | CLK     |       |

1. Referenced to the time at which the output achieves the open circuit condition, not to output voltage levels.

# Write Cycle

| Question          | Decomptor                                           |            | -260 |      | -360 |      | 11-10- |  |

|-------------------|-----------------------------------------------------|------------|------|------|------|------|--------|--|

| Symbol            | Parameter                                           | Parameter  |      | Max. | Min. | Max. | Units  |  |

| t <sub>DS</sub>   | Data In Setup Time                                  |            | 2.1  |      | 2.1  |      | ns     |  |

| t <sub>DH</sub>   | Data In Hold Time                                   |            | 1.6  |      | 1.6  |      | ns     |  |

| +                 | Data lagut ta Draskana                              | Registered | 10   |      | 10   |      |        |  |

| t <sub>DPL</sub>  | Data Input to Precharge Buf                         | Buffered   | 20   |      | 20   |      | ns     |  |

| <b>t</b>          | Data into Active Delay $\overline{CAS}$ Latency (2) | Registered | 4    |      | 4    |      |        |  |

| t <sub>DAL3</sub> | Data into Active Delay (CAS Latency = 3)            | Buffered   | 5    |      | 5    |      | CLK    |  |

| town              | Data into Active Delay (CAS Latency = 2)            | Registered | 4    |      | 4    |      | CLK    |  |

| t <sub>DAL2</sub> | Data into Active Delay (CAS Latency = $2$ )         | Buffered   | 5    |      | 5    |      | ULK    |  |

| t <sub>DQW</sub>  | DQM Write Mask Latency                              | Registered | 1    |      | 1    |      | CLK    |  |

| UQW               | Dam while Mask Latericy                             | Buffered   | 0    |      | 0    |      | ULIX   |  |

#### IBM13M16734JCA 16M x 72 1 Bank Registered/Buffered SDRAM Module

| Symbol              | Parameter                                                     | Min. | Max. | Units | Notes |

|---------------------|---------------------------------------------------------------|------|------|-------|-------|

| f <sub>SCL</sub>    | SCL Clock Frequency                                           |      | 100  | kHz   |       |

| Τ <sub>Ι</sub>      | Noise Suppression Time Constant at SCL, SDA Inputs            |      | 100  | ns    |       |

| t <sub>AA</sub>     | SCL Low to SDA Data Out Valid                                 | 0.3  | 3.5  | μs    |       |

| t <sub>BUF</sub>    | Time the Bus Must Be Free before a New Transmission Can Start | 4.7  |      | μs    |       |

| t <sub>HD:STA</sub> | Start Condition Hold Time                                     | 4.0  |      | μs    |       |

| t <sub>LOW</sub>    | Clock Low Period                                              | 4.7  |      | μs    |       |

| t <sub>HIGH</sub>   | Clock High Period                                             | 4.0  |      | μs    |       |

| t <sub>SU:STA</sub> | Start Condition Setup Time (for a Repeated Start Condition)   | 4.7  |      | μs    |       |

| t <sub>HD:DAT</sub> | Data In Hold Time                                             | 0    |      | μs    |       |

| t <sub>SU:DAT</sub> | Data In Setup Time                                            | 250  |      | ns    |       |

| t <sub>r</sub>      | SDA and SCL Rise Time                                         |      | 1    | μs    |       |

| t <sub>f</sub>      | SDA and SCL Fall Time                                         |      | 300  | ns    |       |

| t <sub>SU:STO</sub> | Stop Condition Setup Time                                     | 4.7  |      | μs    |       |

| t <sub>DH</sub>     | Data Out Hold Time                                            | 300  |      | ns    |       |

| t <sub>WR</sub>     | Write Cycle Time                                              |      | 15   | ms    | 1     |

## Presence Detect Read and Write Cycle

1. The write cycle time (t<sub>WR</sub>) is the time from a valid stop condition of a write sequence to the end of the internal erase/program cycle. During the write cycle, the bus interface circuits are disabled, SDA is allowed to remain high per the bus-level pull-up resistor, and the device does not respond to its slave address.

### **Functional Description and Timing Diagrams**

Refer to the IBM 128Mb Synchronous DRAM Die Revision A datasheet (Document 33L8019.F45415) for the functional description and timing diagrams for buffered-mode operation.

Refer to the IBM Application Notes *Serial Presence Detect on Memory DIMMs* and *SDRAM Presence Detect Definitions* for the Serial Presence Detect functional description and timings.

## Layout Drawing

©IBM Corporation. All rights reserved. Use is further subject to the provisions at the end of this document.

### **Revision Log**

| Rev   | Contents of Modification |

|-------|--------------------------|

| 12/99 | Initial release.         |

#### © Copyright International Business Machines Corporation 1999

All Rights Reserved Printed in the United States of America December 1999

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both. IBM IBM Logo

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351

The IBM home page can be found at http://www.ibm.com

The IBM Microelectronics Division home page can be found at http://www.chips.ibm.com

06K2880.H01193 12/99